# アルテラ・デバイスの PLL回路が提供する利点

TECHNICAL BRIEF 10

1996年7月

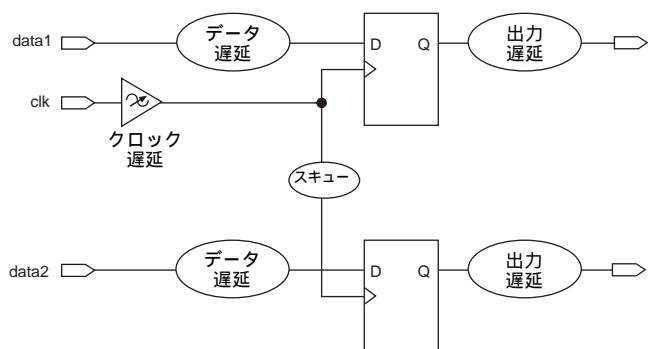

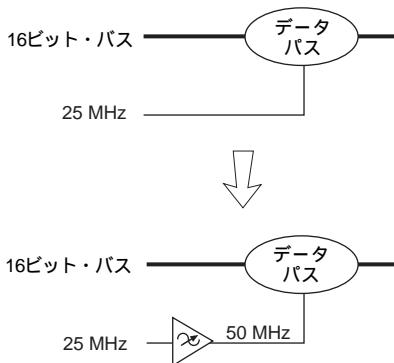

アルテラは、高集積PLDにPLL(Phase-Locked Loop)を使用したClockLockとClockBoostと呼ばれる新しい2つの機能を提供しています。まず、ClockLockの機能はチップ内のクロックのスキーを最小に抑え、性能を大幅に向上させます。また、ClockBoostの機能は入力クロックの周波数を最大4倍まで倍することができ、システムの帯域幅を改善します。これら2つの機能は共にシステム性能と帯域幅の大幅なブレーク・スルーを実現します。図1と図2はClockLockとClockBoostの回路を示したものです。

図1 ClockLockの回路

図2 ClockBoostの回路

ClockLockとClockBoostの革新的な機能は、下記に示されるデバイス内の「Clock-to-Output」の遅延とセットアップ・タイムの式の中の「クロック遅延」、「クロック・スキー」、「データ遅延」の量を大幅に削減します。大規模なデバイスでは、より大きな遅延とスキーが発生する傾向があるため、EPF10K100のような高集積デバイスにはPLL回路の存在が特に重要となります。ClockLockとClockBoostはPLDの性能と使用効率の向上という利点を提供します。

$$t_{CO} (\text{Clock-to-Output遅延}) = (\text{クロック遅延}) + (\text{クロック・スキー}) + (\text{レジスタ遅延}) + (\text{出力遅延})$$

$$t_{SU} (\text{セットアップ・タイム}) = (\text{レジスタ・セットアップ・タイム}) + (\text{データ遅延}) - (\text{クロック遅延})$$

## ClockLock：さらに高速のシステム性能を実現

ClockLockの機能はPLLを使用してチップ内のクロックのスキューを最小にし、性能を大幅に改善します。例えば、FLEX 10KデバイスにClockLockの回路を使用することにより、ワースト・ケースの $t_{SU}$ と $t_{CO}$ はそれぞれ、6nsと3.6nsとなり、システム性能を60%以上も改善することが期待できます。こうした性能の向上は、今後要求される高速のバス・インターフェースなどを実現するときに特に有効です。表1はClockLockによって、改善されるタイミング・パラメータを示したものです。

表1 EPF10K100-3におけるタイミング比較

| タイミング・パラメータ | ClockLock<br>非使用時（暫定） | ClockLock<br>使用時（暫定） |

|-------------|-----------------------|----------------------|

| $t_{CO}$    | 11.5 ns               | 8.5 ns               |

| $t_{SU}$    | 7.0 ns                | 3.6 ns               |

| $f_{SYS}$   | 54 MHz                | 83 MHz               |

## ClockBoost: システムの帯域幅を増加させ、エリアの縮小を実現

ClockBoostはPLLを使用してクロック周波数の倍増機能を実現し、回路の構成に必要なロジックのリソースを大幅に削減します。この使用されるリソースの削減は時分割多重のテクニックを使用して実現されます。例えば、40MHzで動作する32ビットのデータ・バスの機能をデバイス内部で80MHzで動作する16ビットのデータ・バスとして実現することができるため、同じ機能の回路を半分のロジック・リソースとI/Oで構成することができます。表2はClockBoostによって、使用されるロジック・リソースが削減されることを示したものです。

表2 FLEX 10K100において、ClockBoostを利用した場合に達成されるロジック・リソースの削減

| 回路         | ClockBoost<br>非使用時（使用LE数） | ClockBoost<br>使用時（使用LE数） |

|------------|---------------------------|--------------------------|

| 8 × 8 の乗算器 | 330                       | 198                      |

時分割多重を使用した回路が必要ない場合でも、低速のシステム・クロックをアルテラのPLDの内部で倍増して使用することができます。低速のシステム・クロックを使用することによって、プリント基板のレイアウトが簡単になり、クロックの配線パターン上のリンクも小さくなります。

## アルテラ：PLLのリーダー

表3に示すように、アルテラはPLLを内蔵したPLDを供給する唯一のベンダです。ClockLockとClockBoostの機能はアルテラのFLEX 10KとMAX 7000Sの高集積プログラマブル・ロジック・デバイス・ファミリに提供される予定です。

表3 PLL回路が提供されるPLDファミリ

| デバイスの集積度（ゲート数） | Altera                | AMD | Lattice | Lucent | Xilinx |

|----------------|-----------------------|-----|---------|--------|--------|

| 0-25,000       | MAX 7000S<br>FLEX 10K |     |         |        |        |

| 25,000-50,000  | FLEX 10K              |     |         |        |        |

| 50,000-100,000 | FLEX 10K              |     |         |        |        |

---

## 日本アルテラ株式会社

〒163-04 東京都新宿区西新宿2-1-1

新宿三井ビル私書箱261号

TEL. 03-3340-948 FAX. 03-3340-9487

### 本社 Altera Corporation

2610 Orchard Parkway,

San Jose, CA 95134-2020

Telephone : (408) 894-7000

Fax : (408) 944-0952